Risorse del sistema¶

Gli I/O logici sono automaticamente gestiti in immagine di processo dal sistema operativo che provvede a trasferire lo stato di tutti gli ingressi logici nella immagine degli ingressi in memoria di sistema ed a trasferire il valore presente nella immagine delle uscite dalla memoria di sistema alle uscite logiche.

Quindi testando lo stato della immagine di memoria degli ingressi logici si testa lo stato del relativo punto di ingresso (Esempio IX0.0 corrisponde all’ingresso 0 del modulo 0, IX1.5 corrisponde all’ingresso 5 del modulo 1).

Scrivendo lo stato nella immagine di memoria delle uscite logiche si setta lo stato del relativo punto di uscita (Esempio QX0.0 corrisponde all’uscita 0 del modulo 0, QX1.5 corrisponde all’uscita 5 del modulo 1).

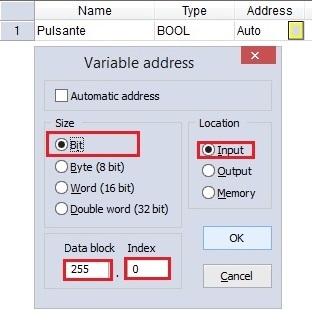

Il modulo CPU è mappato nel blocco di memoria 255, quindi IX255.0 corrisponde all’ingresso 0 del modulo CPU, QX255.1 corrisponde all’uscita 1 del modulo CPU.

LogicLab permette di definire uno mnemonico ai vari I/O digitali, come si vede nella immagine a lato all’ingresso 0 del modulo CPU (IX255.0) viene assegnato il nome Pulsante.

Gli I/O logici possono anche essere gestiti tramite le funzioni SysGetPhrDI e SysGetPhrDO.

Gli I/O analogici sono gestiti tramite le funzioni SysGetAnInp e SysSetAnOut

I contatori sono acquisiti dal blocco funzione SysGetCounter.

Gli ingressi encoder sono acquisiti dal blocco funzione SysGetEncoder.

Il CAN bus viene gestito dalle funzioni SysCANRxMsg e SysCANTxMsg.

Per accedere alle porte seriali occorre utilizzare il blocco funzione SysSerialPort definendo il nome della porta da utilizzare ed i parametri di configurazione della porta. Esistono moduli di estensione che sono provvisti di porte seriali, l’accesso a queste porte è esattamente uguale a quello delle porte presenti sul modulo CPU. Si utilizza la definizione PCOMx.y dove con x si indica l’indirizzo del modulo e con y il numero di porta presente sul modulo. (Esempio PCOM0.0 definisce la porta 0 presente sul modulo 0, PCOM1.2 definisce la porta 2 presente sul modulo 1 e così via).

Per accedere al file system (Sia sul disco interno al sistema che su SD Card) occorre utilizzare la funzione Sysfopen.

Nei modelli provvisti di porta Ethernet è possibile gestire connessioni sia UDP che TCP/IP utilizzando gli appositi blocchi funzione.

Architettura memoria¶

La memoria del sistema è così suddivisa:

| DB | Dimensione | Descrizione |

| IX0 | 32 Bytes | Ingressi logici modulo 00 (R) |

| IX1 | 32 Bytes | Ingressi logici modulo 01 (R) |

| IX2 | 32 Bytes | Ingressi logici modulo 02 (R) |

| IX3 | 32 Bytes | Ingressi logici modulo 03 (R) |

| IX4 | 32 Bytes | Ingressi logici modulo 04 (R) |

| IX5 | 32 Bytes | Ingressi logici modulo 05 (R) |

| IX6 | 32 Bytes | Ingressi logici modulo 06 (R) |

| IX7 | 32 Bytes | Ingressi logici modulo 07 (R) |

| IX8 | 32 Bytes | Ingressi logici modulo 08 (R) |

| IX9 | 32 Bytes | Ingressi logici modulo 09 (R) |

| IX10 | 32 Bytes | Ingressi logici modulo 10 (R) |

| IX11 | 32 Bytes | Ingressi logici modulo 11 (R) |

| IX12 | 32 Bytes | Ingressi logici modulo 12 (R) |

| IX13 | 32 Bytes | Ingressi logici modulo 13 (R) |

| IX14 | 32 Bytes | Ingressi logici modulo 14 (R) |

| IX15 | 32 Bytes | Ingressi logici modulo 15 (R) |

| IX255 | 32 Bytes | Ingressi logici modulo CPU (R) |

| QX0 | 32 Bytes | Uscite logiche modulo 00 (R/W) |

| QX1 | 32 Bytes | Uscite logiche modulo 01 (R/W) |

| QX2 | 32 Bytes | Uscite logiche modulo 02 (R/W) |

| QX3 | 32 Bytes | Uscite logiche modulo 03 (R/W) |

| QX4 | 32 Bytes | Uscite logiche modulo 04 (R/W) |

| QX5 | 32 Bytes | Uscite logiche modulo 05 (R/W) |

| QX6 | 32 Bytes | Uscite logiche modulo 06 (R/W) |

| QX7 | 32 Bytes | Uscite logiche modulo 07 (R/W) |

| QX8 | 32 Bytes | Uscite logiche modulo 08 (R/W) |

| QX9 | 32 Bytes | Uscite logiche modulo 09 (R/W) |

| QX10 | 32 Bytes | Uscite logiche modulo 10 (R/W) |

| QX11 | 32 Bytes | Uscite logiche modulo 11 (R/W) |

| QX12 | 32 Bytes | Uscite logiche modulo 12 (R/W) |

| QX13 | 32 Bytes | Uscite logiche modulo 13 (R/W) |

| QX14 | 32 Bytes | Uscite logiche modulo 14 (R/W) |

| QX15 | 32 Bytes | Uscite logiche modulo 15 (R/W) |

| QX255 | 32 Bytes | Uscite logiche modulo CPU (R/W) |

| MX0 | 512 Bytes | Variabili di sistema sola lettura (R) |

| MX1 | 512 Bytes | Variabili di sistema lettura/scrittura (R/W) |

| MX100 | 4096 Bytes | Memoria utente (R/W). Da indirizzo 2048 a 4095 i dati sono ritentivi. |

Memoria di backup (Retain)¶

SlimLine dispone di 2048 bytes di memoria ritentiva nell’area memoria utente MX100 ed ulteriori 2000 bytes di memoria ritentiva a disposizione utente per allocare variabili mnemoniche.

Le variabili allocate nella memoria utente MX100 da indirizzo 2048 ad indirizzo 4095 sono ritentive, mantengono il loro valore anche allo spegnimento del sistema.

Qualsiasi variabile mnemonica a cui viene attribuito l’attributo RETAIN, manterrà il suo valore anche allo spegnimento del sistema. Da quanto detto precedentemente l’area totale allocabile per le variabili RETAIN è di 2000 bytes.

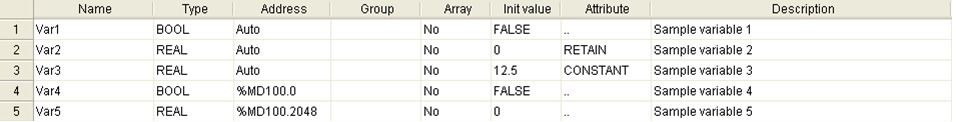

Come si vede dalla foto la variabile Var2 è dichiarata con l’attributo RETAIN e manterrà il suo valore anche allo spegnimento del sistema. La variabile Var5 allocata nella memoria utente MD100.2048 pur essendo ritentiva non necessita dell’attributo RETAIN in quanto è implicito dalla sua allocazione.

Nella finestra di navigazione progetto, tutte le variabili globali sono suddivise in base alla loro definizione, e come si nota nella cartella delle variabili ritentive figureranno solo le variabili mnemoniche Var2 e non le variabili allocate nella memoria utente Var5 pur essendo anch’essa di tipo ritentivo.

Accesso alla memoria¶

IX: Immagine di processo ingressi logici

SlimLine esegue la lettura degli ingressi logici all’inizio di ogni loop di esecuzione programma. E” possibile accedere a quest’area utilizzando variabili di tipo BOOL, ogni indirizzo rappresenta lo stato booleano del relativo ingresso logico. L’indirizzo IX0.0, rappresenta lo stato dell’ingresso 0 del modulo 0, l’indirizzo IX5.12, rappresenta lo stato dell’ingresso 12 del modulo 5.

QX: Immagine di processo uscite logiche

SlimLine esegue la scrittura delle uscite logiche alla fine di ogni loop di esecuzione programma. E” possibile accedere a quest’area utilizzando variabili di tipo BOOL, ogni indirizzo rappresenta lo stato booleano della relativa uscita logica. L’indirizzo QX0.0, rappresenta lo stato dell’uscita 0 del modulo 0,l’indirizzo QX5.12, rappresenta lo stato dell’uscita 12 del modulo 5.

MX: Area di memoria

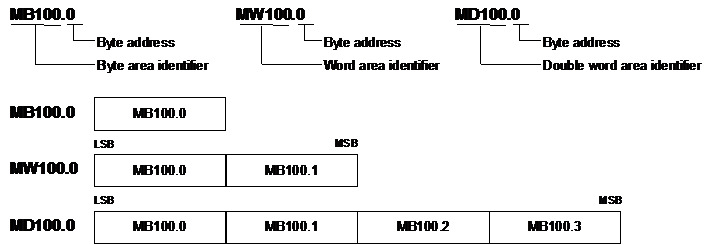

A queste aree è possibile accedere utilizzando tutti i tipi di variabili definiti. Siccome tutte le variabili utilizzano la stessa area di memoria, occorre prestare attenzione alla dimensione in bytes del tipo definito per evitare sovrapposizioni di indirizzo.

Ad esempio una variabile DWORD allocata ad indirizzo MD100.10 utilizzerà anche lo spazio di memoria MB100.11, MB100.12 ed MB100.13. Quindi allocando una variabile BYTE all’indirizzo MB100.11 si andrebbe ad occupare uno spazio di memoria già utilizzato dalla variabile precedente.

E” comunque possibile allocare variabili sovrapponendone l’indirizzo, esempio allocare due variabili BYTE sugli stessi indirizzi di una variabile WORD per andarne a considerare la parte MSB od LSB. Oppure allocare due variabili WORD sugli stessi indirizzi di una variabile DWORD per andarne a considerare la parte MSW od LSW. Riporto una semplice tabella esplicativa.

|

Attenzione! SlimLine è basato su architettura ARM e questo tipo di architettura assume che:

Le variabili a 16 bits, WORD, INT, UINT siano allocate in memoria ad indirizzi divisibili per 2. Quindi una variabile a 16 bits potrà assere allocata ad esempio ad indirizzo MW100.32 ma non ad indirizzo MW100.33.

Le variabili a 32 bits DWORD, DINT, UDINT, REAL siano allocate ad indirizzi divisibili per 4. Quindi una variabile a 32 bits potrà assere allocata ad esempio ad indirizzo MD100.32 ma non ad indirizzo MD100.33, MD100.34, MD100.35.

Questa regola viene applicata automaticamente dal compilatore di LogicLab anche per quanto riguarda le strutture dati, quindi nella definizione di una struttura dati composta da variabili di tipo eterogeneo LogicLab inserirà automaticamente dei bytes di spaziatura per allineare correttamente le variabili di a 16 bits ed a 32 bits.